本文来自微信公众号“与非网eefocus”,作者/刘洪。

日前有媒体爆出,苹果正小批量试产采用先进封装3D堆叠技术的系统整合芯片(SoIC),计划采用SoIC搭配集成扇出(InFO)封装方案,预计最快将2025-2026年用在MacBook上。

先进封装是下一代集成电路的关键基础,涵盖小芯片(Chiplet)、倒装(FlipChip)、凸块(Bumping)、晶圆级封装(WLCSP,如FOWLP(扇出晶圆级封装)、扇出型板级封装(FOPLP)、2.5D封装(如interposer(中介层)、RDL(重布线层)等)、3D封装(如TSV(硅通孔))、封装天线(AiP)等先进封装技术。

受人工智能(AI)、数据中心、自动驾驶汽车、5G等HPC(高性能计算)和网络市场采用超高密度封装的推动,特别是AI和HPC应用的不断成熟,对数据传输的需求正继续增加,进而对半导体行业产生了强烈影响,推动了对创新封装解决方案的需求。

未来,作为先进封装的主战场,FOWLP的产量仍将主导市场。而作为先进封装一个重要的分支,扇出型(FO)封装正在渗透到远大于每平方毫米18个的更高的I/O密度,同时实现更精细的RDL,将线宽/线距(L/S)尺寸微缩到5μm/5μm以下。其中超高密度扇出(UHDFO)封装增长最快、高密度扇出(HDFO)和单芯片扇出封装(Core FO)也是发展方向。我们来看看,有哪些厂商和技术将引领FO市场的发展。

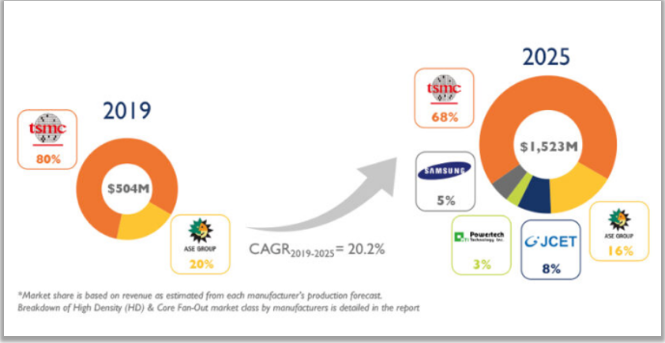

制造商预测的超高密度扇出收入

九成以上FO市场群雄占据

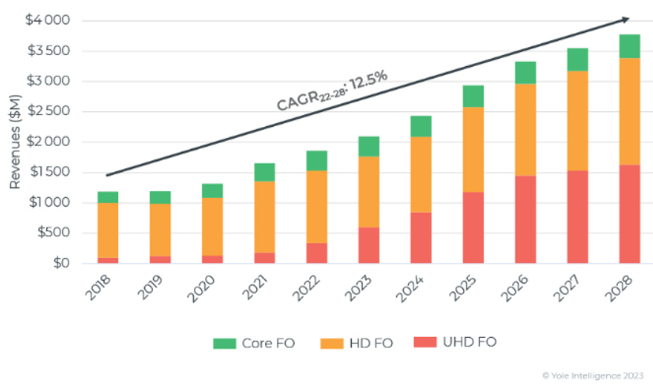

Yole Intelligence数据显示,2022年,FO收入为18.6亿美元,预计到2028年将达到38亿美元,复合年增长率为12.5%。增长最快的UHDFO复合年增长速度为30%,将从2022年的3.38亿美元增长到2028的16.30亿美元。

Yole Intelligence技术和市场分析师Gabriela Pereira表示,HDFO已经是2022年的主要市场,收入为11.94亿美元,复合年增长率为6.7%,2028年将达到17.57亿美元。Core FO的复合年增长率为2.8%,从2022年的3.29亿美元增至2028年的3.89亿美元。

2018-2028 Core FO/HDFO/UHDFO封装收入

他认为,FOWLP的产量仍将主导市场,2028年的晶圆产量将达到2376K片,而FOPLP的300mm晶圆当量产量为238K片。FO封装总量将从2022年的23.48亿个增长到29.6亿个。

台积电是高端计算、网络和HPC应用的高性能FO解决方案的市场领导者,占有76.7%的市场份额。2022年,台积电与前三大外包半导体组装和测试(OSAT)公司日月光(ASE)、Amkor和JCET共占据90%以上的FO市场。为了追赶台积电,ASE、矽品(SPIL)、三星、JCET、Amkor、PTI、TFME和Nepes都在开发具有竞争潜力的类似解决方案。尽管Core FO是OSAT的主要市场,但主要发展方向是HD和UHDFO技术。

中国OSAT加速渗透FO供应链

天灾人祸之下供应中断,芯片制造业的区域独立正成为一种趋势。过去的五年里,中国投资先进封装技术的力度越来越大,许多公司正在进入FOWLP或FOPLP业务。

由于能够实现无基板(no-substrate)解决方案,在芯片和衬底短缺的情况下,扇出技术广受欢迎。小芯片和异构集成已经成为利用较为成熟的光刻制造节点的手段。因此,随着美国对先进工艺技术实施限制,先进封装已成为中国公司市场竞争的战略之一。

大多数中国OSAT投资的重点首先放在了低密度封装上,这将有助于实现更快的投资回报。一些新的中国OSAT正在渗透FO封装供应链,如奕成科技、中科智芯和厦门云天、华润微、易卜半导体、佛智芯等。这些公司为拓展先进封装能力的投资超过了25亿美元。

2022中国FO封装格局

小芯片和异构集成推动FO发展

在HPC、网络、汽车和高端移动市场应用的推动下,FO封装已从低端封装技术发展成为高性能集成平台。该技术的主要市场趋势之一是将大型芯片划分为小芯片并进行异构集成。FO是一个经济高效的平台,可通过基于RDL的工艺实现高带宽和高密度的芯片对芯片(D2D)互连。未来,UHDFO将通过创新的板级扇出型封装(FOCoS)和FO嵌入式桥接解决方案从硅中介层获得市场份额。

不过,Yole Intelligence也指出,虽然FOPLP被称为广泛采用FO的解决方案,特别是对于大封装尺寸,但它仍然存在技术挑战,并且缺乏实现所需成本效益的需求。

适合不同需求和特点的不同应用的FO

高性能FO日渐走红

领先的IC代工厂已经在交付7nm和5nm晶圆,3nm产品尚处于认证阶段。由于高晶体管密度需要更昂贵的工艺来制造,晶圆成本持续飙升。即使随着新节点的出现,缺陷密度可以保持相对平坦,但硅的单位面积成本也会非线性增加,因此,新的封装技术已纳入了未来产品架构当中。

1

扇出+桥接

在扇出工艺流程中,近年来FOCoS备受青睐。前不久,日月光推出FOCoS-Bridge大型封装技术,将多个小芯片封装在一个基板上,实现了10颗小芯片高速互联。

FOCoS-Bridge是日月光VIPack封装平台的一部分,也是2.5D封装技术的改良版,可以满足未来AI和HPC应用对更高带宽、更高速度芯片不断增长的需求。日月光利用高度集成的扇出结构优势克服了传统电气互连的局限性,并实现处理器、加速器和内存模块之间的高速、低延迟和节能数据通信。

FOCoS-Bridge技术的实现是在芯片基板上先放置一个用于小芯片间互连的独立硅芯片,在此基础上构建铜连接层,经加工暴露触点后,将需要互连的小芯片以倒装方式封装在基板上实现互连。这种方式可以将1颗ASIC处理器与4颗高带宽存储器(HBM)封装在一起,组成47×31mm的单元。然后,再将两个单元并排封装在一起,组成一个大型芯片,实现包含2颗专用集成电路(ASIC)处理器、4颗HBM及8颗封装内互连小芯片的完整封装。

所谓FOCoS-Bridge是一种用于实现小芯片集成的硅桥技术,利用封装内小芯片之间互连路由层集成微小硅片,如图形计算芯片(GPU)和HBM。硅桥嵌入在扇出RDL层中。

FOCoS-Bridge是采用硅中介层的2.5D封装的替代品。与2.5D一样,硅桥在封装中提供超细间距互连,以解决系统中的内存带宽瓶颈挑战。与2.5D相比,FOCoS-Bridge的优势在于只在将两个小芯片连接在一起的区域使用硅片。

FOCoS-Bridge的制作工艺是将具有微凸点的待嵌入硅桥芯片连接到载片(wafer carrier)上,然后在上面镀Cu柱。随后的第一成型工艺是研磨成型以暴露Cu柱和微凸块,然后在其上形成RDL层。之后,连接ASIC和HBM芯片,进行底部填充和二次成型。移除载片并形成凸块后,将模制晶圆锯成单独的扇出封装。最后使用传统的倒装芯片工艺将扇出封装连接到有机基板上。

FOCoS-Bridge制作工艺

该技术的好处在于提供了与硅中介层解决方案类似的电气、信号和功率完整性性能,但成本较低,且没有掩模版尺寸限制。其设计具有高度可扩展性,能够无缝集成到复杂的芯片架构中,同时提供具有亚微米L/S、高I/O数和高速信号传输的高密度D2D互连,以满足不断发展的AI和HPC需求。

硅桥芯片的使用使芯片边缘线性密度比传统的有机倒装芯片封装高一个数量级。此外,FOCoS-Bridge为在扇出封装中嵌入无源和有源芯片奠定了基础,并提供了去耦电容器集成选项,有助于功率传输优化,并直接访问某些功能(如存储器、I/O等)的有源芯片。

该技术可以更高效地利用计算资源,加速数据密集型工作负载,并有助于推进AI算法、深度学习、科学模拟和其他计算要求高的任务。其应用包括AI、数据中心、服务器和网络应用的多芯片和HBM集成,以及APU/CPU/GPU的内存和无源集成,还有AI、数据中心、移动、自动处理器、通信基础设施和网络应用的小芯片。

矽品的扇出嵌入式桥接(FOEB)技术创造了一种根据需要将桥接晶片放置在小芯片或存储模块下方,从而提供硅密度的D2D互连的方法。桥接本身嵌入在封装中,补充了多层扇出金属化(fan-out metallization)。金属化提供封装微缩工艺路线,而通孔通过桥接层提供垂直互连。该技术与日月光的方法有异曲同工之处。

嵌入式桥接(FOEB)

FOEB的优点是采用模塑料桥接技术,具有高IO/高带宽、细线/多层RDL可路由性。其目标应用同样是高性能计算、网络和数据服务器的高端应用。

2

高密度互连

异构封装一直是业界想要的答案,但直到最近这种设计方法才变得实用。原本是单个芯片的系统级芯片(SoC)现在正从同质设计中分离出来,并在更小的独立硅芯片中创建。一个趋势是去除与存储器通信的I/O块及长距离串行/解串器(SerDes),以创造一个电气、功能、物理的构建块,使IC功能块可以重复使用。

最新进展始于2.5D硅通孔(TSV)产品,在同一IC封装中与ASIC一起实现非常高密度的DRAM存储器或HBM。Amkor的HDFO解决方案就是一种优化性能和成本的异构IC封装。

使用小芯片实现异构结构的IC封装在很大程度上受到小芯片之间通信接口的影响。对许多应用来说,要选择芯片之间IO为100s或1000s的高速并行接口,就需要高密度互连。

Amkor开发的基板硅晶圆集成扇出(S-SWIFT)或桥接技术(S-Connect)2.5D TSV的HDFO解决方案,实现了细线布线至2µm线宽、2µm间距和6层结构。这种模块制造技术可以实现小芯片和HBM的集成。S-Connect是HDFO和桥接的组合产品,目前正处于内部鉴定阶段。

芯片对芯片接口选择使封装差异化

S-SWIFT利用Cu细线光刻和有机电介质实现现场制造的高水平信号布线密度。S-Connect很少使用高密度RDL技术,但增加了高密度桥接,有助于实现小芯片之间的高密度路由。使用Cu混合键合提供的超密集垂直D2D互连的3D芯片堆叠在未来也将优化2D集成。

先进封装解决方案

HDFO是头部公司的一场战争

早在2018年,三星电机(SEMCO)的FOPLP工艺对FO封装市场产生了积极影响。三星在其智能手表中采用HDFOPLP是一个关键的里程碑。目前,HDFO基本上只由苹果的应用处理器引擎(APE)驱动,该引擎使用台积电的inFO_PoP制造。另一方面,三星正在其豪华和高端智能手机中实现HDFOPLP的商业化。因此,到2025年,三星将创造21%的HDFO市场份额。问题在于,三星能否在尽可能短的时间内实现成本降低。

AMD发布的GPU小芯片设计新专利提出了一种新设计方案——将一个大型单片GPU拆分为几个小芯片,并使用FO技术连接不同的芯片,但在基板上方添加一个小硅桥来连接两个芯片,AMD称其为高架扇出桥2.5D。

高架扇出桥2.5D

苹果工作站M1 ultra则使用了台积电的扇出技术。M1 Ultra芯片将两个M1 Max芯片组与1140亿个晶体管、一个20核CPU和一个64核GPU集成在一起,在消耗相同功率时,多线程性能比最快的16核台式机高出90%,性能也比目前市场上最快的台式机GPU快,功耗低200W。其UltraFusion D2D连接实现2.5TB/s的带宽,包括两个并行M1 Max SoC的通信。

不过,M1 Ultra并不是在台积电CoWoS-S(带硅中介层的晶圆上芯片)2.5D封装上大规模生产的,而是采用本地硅互连(LSI)的InFO,更具成本效益。

台积电消费电子HDFO解决方案

一切为了降本增效

FO封装技术可以生产出高性能的半导体器件,同时增加I/O数量,前景一片光明。随着行业在异构IC封装路线图方面不断取得进展,以及硅架构灵活性的提高、小芯片的重复使用、上市时间的缩短和总体成本的降低,FO将继续推动封装行业的持续创新和发展。