本文来自半导体行业观察,作者/编辑部。

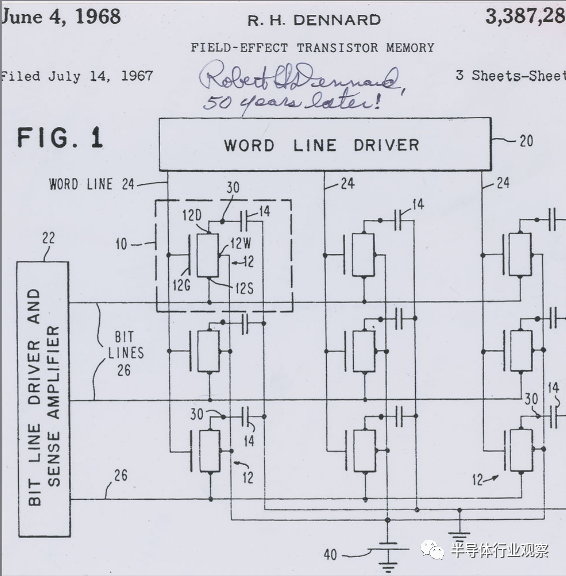

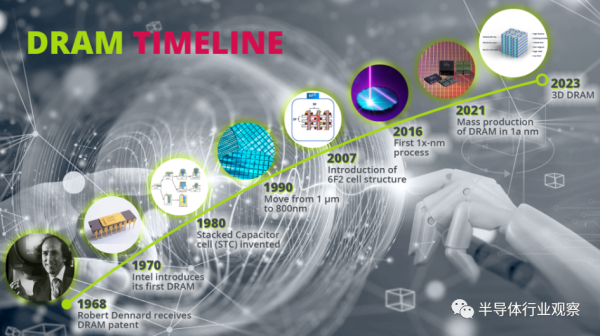

1968年6月4日,Robert Dennard获得了单晶体管、单电容器DRAM单元设计理念的专利。这在今天听起来并不惊天动地,但在六十年代,这是一种激进的新方法。

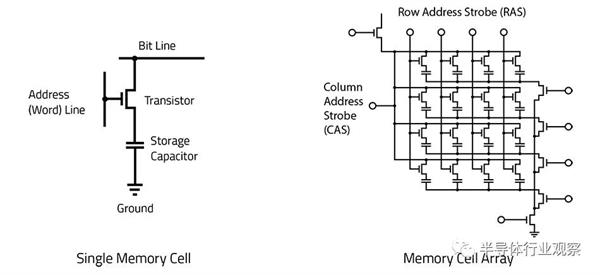

从1966年开始,Robert Dennard就试图创建一种SRAM和磁芯存储器的替代方案,前者都每个数据位都需要有6个MOS晶体管,或者需要一个半硬铁氧体磁芯环。他观察到MOS技术能够构建电容器,从而得出结论:一个晶体管和一个电容器就足以构成存储芯片。这种简单的结构至今仍是DRAM的构建方式。

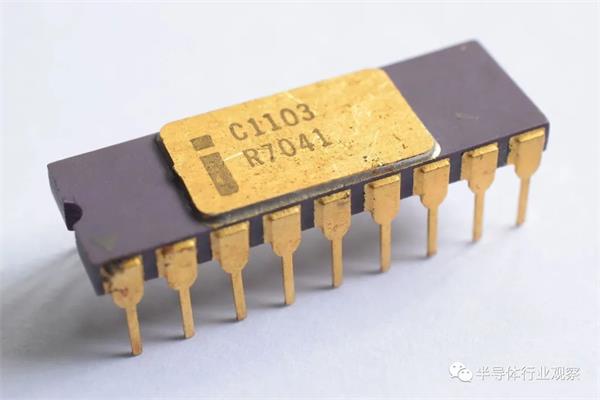

早在1969年,Advanced Memory System就将其第一款MOS DRAM芯片商业化,但将1024位芯片出售给霍尼韦尔,而霍尼韦尔又要求英特尔基于其开发的三晶体管单元制造DRAM。由于这款三晶体管1102 DRAM存在诸多问题,英特尔自行设计并于1970年10月推出了第一款i1103 DRAM,这是第一款商用且成功的DRAM IC。

DRAM是如何工作的?

尽管1晶体管1电容的结构非常简单,DRAM在发展初期也遇到了麻烦。事实上,英特尔推出的前五代DRAM的良率非常低,因为DRAM单元的模拟特性才刚刚开始显现。虽然存储单元本身包含数字信号(0或1),但为了产生数字信号,必须读出、放大并写回模拟信号。为了理解这意味着什么,让我们看看DRAM结构。

DRAM单元以规则的矩形、网格状图案布局,以便于通过字线和位线对其进行控制和访问,并且需要感测放大器来读取DRAM单元中包含的状态。初始放大后,信号需要在芯片上快速长距离传输,再次需要第二次模拟传感放大过程。当存取晶体管被激活时,电容器中的电荷与位线共享。位线的电容比电容器的电容大得多(大约十倍)。因此,位线电压的变化是微小的。需要检测放大器将电压差分解为逻辑信号系统指定的电平。这都是非常类似的行为。

但最初的DRAM设计者必须解决的问题是连接和感测单元时的传播延迟,这些问题需要以模拟方式精确计时,并考虑到最远位置最慢的单元。如果时序不正确且太早或太短,信号可能会翻转到错误的方向,或者写回存储单元的信号太弱。

经过几位测试、设计和产品工程师的详细分析才解决了这些问题,但在那之后,DRAM的成功故事就开始了。英特尔i1103也被称为“核心杀手”,因为它非常成功地取代了传统的基于铁氧体核心的存储单元。

缩放就是一切

当笔者在20世纪80年代末开始涉足半导体行业时,行业正在研究5000纳米工艺的DRAM。工作人员会打印出掩模,或者更确切地说,将它们绘制在箔片上,然后我们使用简单的相机将它们缩小100倍。如今,我们采用12纳米工艺,最轻微的污染都会影响蚀刻并破坏cell。

过去几年我们所看到的规模扩张令人惊叹。Intel 4004处理器的运行频率为740kHz,比当今的处理器和DRAM接口慢200万倍。如今,我们拥有16Gb单芯片,比第一代DRAM多1600万倍。

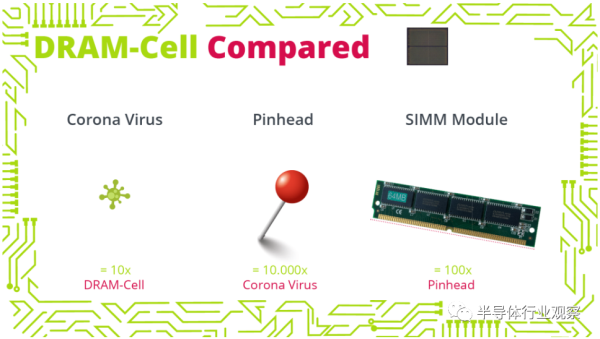

您是否知道,利用当今的处理节点,您可以将10个DRAM单元压缩到1个冠状病毒中?如今,存储单元非常小,只能容纳10,000个电子。它们是微小而精致的结构,必须被拉到粗糙的位线上来检查它们的负载是0还是1。考虑到这一点,它们能够可靠地工作,而且DRAM和闪存大约占全球所有半导体销售的30%,这实际上是一个小奇迹。如今,它们在火星漫游车、彗星着陆设备上运行多年,基本上成为地球上所有电子设备的一部分。

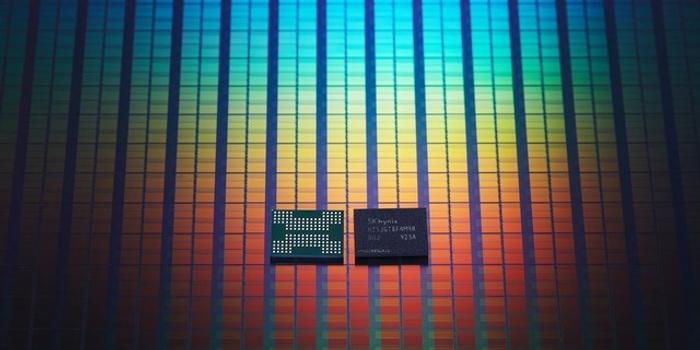

现在,三星、SK海力士和美光也成为全球领先的三大DRAM龙头,他们把持着全球大部分的DRAM市场份额,他们的技术也进入到12nm的级别。

今年五月,三星宣布,其采用业界最先进的12纳米(nm)级工艺技术的16 Gb DDR5 DRAM已开始量产。与上一代相比,三星全新12纳米级DDR5 DRAM功耗降低高达23%,同时晶圆产能提高高达20%。其出色的能效使其成为希望降低服务器和数据中心能耗和碳足迹的全球IT公司的理想解决方案。

三星12纳米级工艺技术的开发之所以成为可能,是因为使用了有助于增加cell电容的新型高κ材料。高电容会导致数据信号中产生显著的电势差,从而更容易准确地区分它们。该公司在降低工作电压和降低噪音方面的努力也有助于提供客户所需的最佳解决方案。

三星的12纳米级DDR5 DRAM系列拥有每秒7.2吉比特(Gbps)的最大速度,即可以在大约一秒内处理两部30GB超高清电影的速度,将支持越来越多的应用,包括数据中心、人工智能和下一代计算。

与此同时,韩国的SK海力士也对外表示,公司已完成现有DRAM中最为微细化的第五代10纳米级(1b)技术研发,并将适用其技术的DDR5服务器DRAM提供于英特尔公司(Intel®)开始了“英特尔数据中心存储器认证程序(The Intel Data Center Certified memory program)”。

据介绍,SK海力士向英特尔提供的DDR5 DRAM产品运行速度高达6.4Gbps(每秒6.4千兆比特),公司技术团队实现了目前市面上DDR5 DRAM的最高速度。与DDR5 DRAM初期阶段的试制品相比,数据处理速度提升了33%。

SK海力士进一步指出,公司在此次1b DDR5 DRAM上采用了“HKMG(High-K Metal Gate)”工艺,与1a DDR5 DRAM相比功耗减少了20%以上。

美光在去年11月初则表示,公司正在向部分智能手机客户运送其1-beta DRAM的合格样品,并已做好大规模生产的准备。而在美光看来,公司的1-beta DRAM的推出标志着内存创新的又一次飞跃,这是其专有的多重图案光刻技术与领先的工艺技术和先进材料能力相结合所带来的。

美光科技透露,凭借业界首创的1β节点,公司可在更小的占地面积内实现更高的内存容量,从而降低每比特数据的成本。DRAM的扩展在很大程度上是通过每平方毫米半导体面积提供更多、更快的内存的能力来定义的,这需要缩小电路以在指甲盖大小的芯片上容纳数十亿个存储单元。对于每个工艺节点,半导体行业几十年来每一两年都会缩小器件尺寸。然而,随着芯片变得越来越小,在晶圆上定义电路图案需要挑战物理定律。

美光指出,1-Beta LPDDR5X每芯片容量为16Gb,比上一代产品高出35%,并且与上一代产品相比节能15%。能获得这样的突破,是新节点在新工艺、材料和设备支持下取得的成果。未来,美光可以积极扩展存储单元阵列的尺寸以及染料中其余电路的尺寸,以节省空间。

下一步是什么?

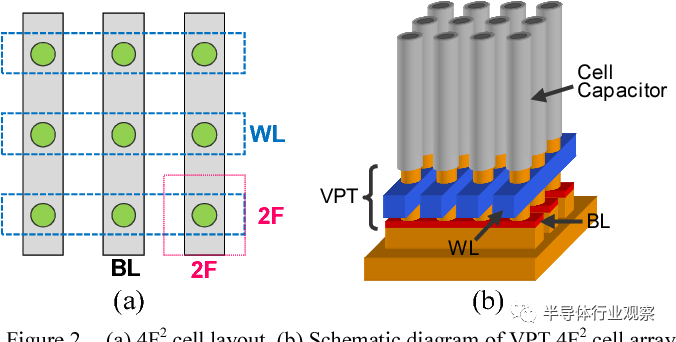

对于传统DRAM未来的发展,如Techinsights所说,到目前为止,我们已经看到了8F2和6F2 DRAM Cell设计,其中unit cell包括1T(晶体管)和1C(电容器)。这种1T+1C单元设计将用于未来几代DRAM的DRAM单元设计。然而,由于工艺和布局的限制,DRAM厂商一直在开发4F2单元结构,例如1T DRAM或无电容器DRAM原型,作为下一个扩展DRAM技术的候选者之一。

对于10nm级及以下的DRAM单元设计,应该加入更多创新的工艺、材料和电路技术,包括High-NA的EUV、4F2、1T DRAM、柱状电容器(pillar capacitor)、超薄更高k电容器电介质和低-k ILD/IMD材料。

此外,3D DRAM被誉为下一个重大事件。但从存储晶体管器件的发展中面临的挑战以及对超低泄漏DRAM要求的极端要求,我很难想象这种情况会在短期内发生。在过去30年里,行业也一直在努力寻找堆叠解决方案。由于您正在处理多晶硅并且现在具有低泄漏或严格的浮动晶体管要求,因此在闪存中堆叠更容易。FLASH原理只是基于捕获电荷引起的阈值电压变化。但在DRAM中,您需要具有完美低泄漏行为且无浮动块的单晶结构来完美切换存储单元晶体管,因此DRAM可以以最小泄漏关闭,以将电荷保持64毫秒。

例如据韩媒TheElec获悉,三星已经组建了一个团队来开发4F2 DRAM。消息人士称,如果这家科技巨头成功,与6F2 DRAM相比,它能够将裸片表面减少30%。

十年前,内存芯片制造商试图将4F2商业化,但当时失败了。但现在三星认为,与竞争对手SK海力士和美光正在开发的3D DRAM相比,这种结构更容易实现。三星的目标是开始将4F2结构应用于10纳米(nm)或以下节点制造的DRAM,因为它认为从那时起它可以将通道长度缩小多少是有限的。

三星的4F2旨在让晶体管垂直向上。它要从下到上放置源极、栅极、驱动器和电容器。连接字线和位线将使它们的尺寸分别为2F和4F。这将是一个全新的结构。报道指出,在10nm以下,三星会推出一代4F2;下一代将使用直接粘合来制作2层。

虽然大家都在探索不同的路劲,但3D DRAM仍然在激励工程师想出新的方法。

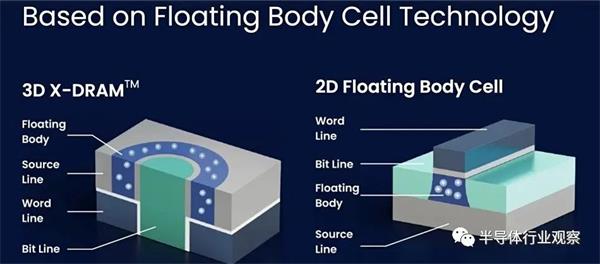

例如一家名为NEO Semiconductor的初创公司认为,它已经找到了一种方法,可以通过其3D X-DRAM技术实现这一目标。该概念具有基于无电容器浮体单元(FBC)技术的类3D NAND DRAM单元阵列结构。这种FBC技术使用一个晶体管和零个电容器将数据存储为电荷。NEO表示它可以使用当前的3D NAND类工艺制造,并且只需要一个掩模来定义位线孔并在孔内形成单元结构。这提供了一种高速、高密度、低成本和高产量的制造解决方案,这是一个重要的主张。

不用很久的未来,相信我们很快就会看到3D DRAM是否会取得突破。因为毕竟过去的55年已经展现了DRAM无限的创新力量。