本文来自微信公众号“半导体行业观察”,作者/杜芹DQ。

存储器是现代信息系统的关键组件之一,其应用广泛,市场庞大。由DRAM与NAND Flash所主导的主导的传统存储市场规模已超过1600亿美元,而且长远来看,DRAM和NAND仍将占据主流市场很久。那么存储技术发展到现在,这两大主流的传统存储技术背后的供应商们都在比拼什么?

NAND Flash厂商在拼什么?

一、拼层数,盖高楼

几十年来,NAND Flash一直是低成本和大密度数据存储应用的主要技术。这种非易失性存储器存在于所有主要的电子终端市场,例如智能手机、服务器、PC、平板电脑和USB驱动器。NAND Flash的成功与其不断扩展存储密度和成本的能力有关,大约每两年,NAND Flash行业就能够大幅提高位存储密度,现在位存储密度的进一步增加是通过向三维过渡,2014年,3D NAND技术进入市场。而为了维持NAND Flash路线图,3D NAND Flash进入了层数的堆叠比拼。

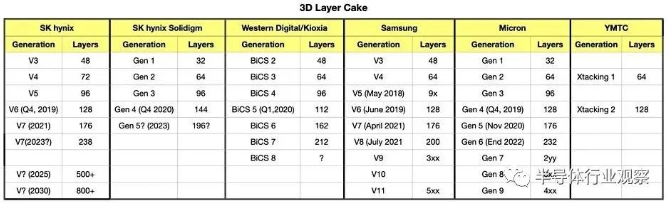

2022年是NAND闪存的35周年,而今年或许是NAND闪存又一个重要的一年。现在几乎头部的存储厂商都在制造200层以上的存储芯片,甚至500层已经陆续出现在存储厂商们的路线图中。闪存芯片中的层数越多,容量就越高。下表显示了几大NAND制造商的3D NAND的层数的主要计划:

图源:blocks&files

在NAND FLash领域,三星电子将在2022年底推出200层或更多层的第8代NAND闪存。据businesskorea的报道,有业内人士认为,三星已经通过“双栈”的方式获得了256层技术。用于连接单元的孔越少,芯片丢失的数据就越少。因此,单栈技术比双栈技术更先进。然而,100层被认为是单栈技术的技术极限。目前,三星电子是世界上唯一一家可以使用单堆叠方式堆叠超过100层(128层)的芯片制造商。全球第二大NAND闪存生产商SK海力士和美国美光科技一直在使用双堆栈技术堆叠72层或更多层。

业内人士预测,三星电子将加快200层以上NAND闪存的量产步伐,他们表示三星电子将成为第一家通过在128层单堆栈中增加96层来发布224层NAND闪存的芯片制造商。与176层相比,224层NAND闪存的生产效率和数据传输速度将提高30%。

美光正在批量生产176层的闪存芯片,这是其第五代3D NAND。3D NAND是通过在垂直堆栈中将多组单元相互层叠来制造的。美光近日表示,其正在开发232层的3D NAND,并声称其232层技术代表了世界上最先进的NAND,路线图规划到了500层(但没具体指明时间表)。

美光的232层NAND芯片采用3D TLC架构,原始容量为1Tb(128GB)。该芯片基于美光的CuA(CMOS under array)架构,并使用NAND串堆叠技术在彼此之上构建两个3D NAND阵列。CuA的设计加上232层的NAND将大大减少美光1Tb 3D TLC NAND存储器的裸片尺寸,这将降低生产成本,使美光能够具有芯片定价权。

(图片来源:美光)

西部数据和铠侠近日表示,他们正在构建162层的NAND,该公司计划在2022年底推出其第6代BiCS。西部数据声称他们将通过使用新材料来缩小存储单元的尺寸,从而缩小芯片尺寸。西部数据计划将这些芯片用于从USB驱动器到PCIe 5.0 SSD的等多种产品中。

资料来源:西部数据

此外,西部数据还将于2024年推出具有超过200层的BiCS+内存,与BiCS6相比,它的每个晶圆的位数将增加55%,传输速度提高60%,写入速度提高15%。值得注意的是,BiCS+仅用于数据中SSD,因为该公司计划为消费者存储提供不同级别的2xx层NAND,称为BiCS-Y。除此之外,西部数据还表示,他们正在研究多种技术以提高密度和容量,包括PLC,并计划在2032年构建500层以上的NAND。

SK海力士在200层的跨越上可能稍微晚些,目前为止SK海力士最新的3D NAND是512Gb 176层堆叠的3D NAND,不过早在去年3月份的IEEE IRPS上,SK海力士CEO李锡熙就已经展望到600层。

国内方面主要竞争者是长江存储,长江存储这几年的发展很快,此前长江存储CEO杨士宁层表示:“长江存储用短短3年时间实现了从32层到64层再到128层的跨越。长江存储3年完成了他们6年走过的路”。而现在,据Digitimes的报道,业内人士透露,长江存储最近已向少数客户交付了其内部开发的192层3D NAND闪存样品。

这些巨头厂商清晰明确的NAND路线图也证明了NAND和SSD市场的技术健康和活力。总体而言,NAND闪存供应商都准备在2022年底至2023年之间推出其200层以上的芯片产品,这是该行业向更高密度3D NAND闪存过渡的里程碑。

二、拼资本支出,拼产能

对于存储厂商来说,重资本是行业的特点,产能的保障也是企业保持致胜的一大关键。而随着NAND闪存供应商加入200层以上NAND闪存芯片的竞争,必将需要新的晶圆厂和新设备。

IC Insights预测今年NAND闪存资本支出将增8%至299亿美元,超过2018年278亿美元的历史新高。闪存资本支出在2017年飙升,当时该行业向3D NAND过渡,此后每年资本支出都超过200亿美元。299亿美元的支出占2022年整个IC行业1904亿美元资本支出预测的16%,仅落后于代工部门,该部门预计将占今年行业资本支出的41%。

来源:IC insights

新的和最近升级的NAND闪存工厂包括三星的平泽P1和P2(也用于DRAM和代工),以及三星在中国西安的二期投资;铠侠在日本岩手的Fab 6(Flash Ventures)和Fab K1;美光在新加坡的第三家闪存工厂。SK海力士为其M15工厂的剩余空间配备了NAND闪存。

此外,据TheElec获悉,三星计划于今年5月初在其平泽工厂的新先进晶圆厂P3上安装晶圆厂设备,该公司的目标是在今年下半年内完成工厂的建设,消息人士称,三星将首先在5月的第一周为NAND闪存生产安装晶圆厂设备。P3是一家混合工厂,将同时生产存储芯片和逻辑芯片,其中就包括第七代176层V-NAND芯片。预计三星未来几年将在P3上花费至少30万亿韩元到近50万亿韩元。

而SK海力士也在大连建设新的3D NAND闪存晶圆厂,该项目于5月16日开工。2021年底,SK海力士完成了收购英特尔NAND闪存及SSD业务案的第一阶段,从英特尔手中接管了SSD业务及其位于大连的NAND闪存制造厂的资产。为加快推动项目发展,所以SK海力士决定在大连继续扩大投资并建设新工厂。

DRAM厂商拼什么?

不可不争的EUV

随着DRAM要想进入到10nm工艺一下,EUV俨然已成必不可少。我们也看到,三星、SK海力士和美光这三大DRAM厂商已经先后拥抱了EUV技术。

三星电子基于极紫外(EUV)光刻技术的1z-nm工艺的DRAM已于今年2月份完成了量产。半导体分析机构TechInsights拆解了采用EUV光刻技术和ArF-i光刻技术的三星1z-nm工艺DRAM,它认为该技术提升了三星的生产效率,并减小了DRAM的核心尺寸。DRAM单元尺寸和D/R缩放最近越来越难,但三星将D1z的D/R降低到15.7 nm,比D1y缩小了8.2%。据了解,三星还将继续为下一代DRAM增加EUV步骤。上文中提到的三星的P3工厂也将采用EUV工艺生产10nm DRAM。

三星DRAM单元尺寸趋势,D3x到D1z

(图源:TechInsights)

美光有望从2024年开始生产基于极紫外(EUV)光刻工艺的DRAM芯片,在1γ(Gamma)节点的有限的层数中部署EUV,然后会将其扩展到具有更大层采用率的1δ(Delta)节点。旨在通过允许制造更小的芯片特征来保持摩尔定律的存在。这一举措有望帮助其在技术上保持领先于竞争对手。

SK海力士也引入了EUV光刻设备来解决以往DUV光刻的局限性,制程工艺能轻松达到10nm以下,以此来提升生产效率。2021年2月1日,SK海力士完成首个用于DRAM的EUV晶圆厂M16,并引进了EUV光刻设备。2021年7月,SK海力士宣布量产了1anm工艺的8千兆的LPDDR4 EUV DRAM。

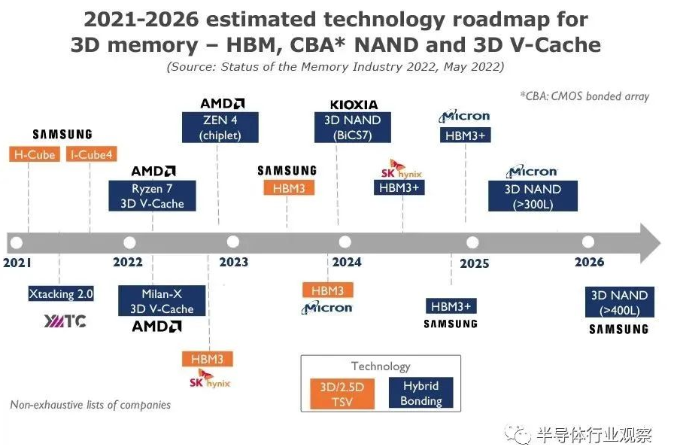

3D堆叠成为DRAM新未来

但是对于DRAM来说,目前业界的共识或者面临的挑战是,在平面工艺下,DRAM最重要也最艰难的挑战,就是储存电容的高深宽比,储存电容的深宽比通常会随着组件工艺微缩而呈倍数增加,也就是说,平面DRAM的工艺微缩会越来越困难,即使是通过极紫外光刻(EUV)工艺,也不足以为整个未来十年提供所需的位密度改进。因此,主要设备供应商和领先的DRAM制造商正在考虑将单片3D DRAM(类似3D NAND)作为长期扩展的潜在解决方案。

据了解,3D DRAM是将存储单元(Cell)堆叠至逻辑单元上方以实现在单位晶圆面积上产出上更多的产量,这样3D DRAM就可以有效地解决平面DRAM的挑战。除了晶圆的裸晶产出量增加外,使用3D堆叠技术也能因为可重复使用储存电容而有效降低DRAM的单位成本。

在这其中,HBM(High Bandwidth Memory,高带宽存储器)技术可谓是DRAM从传统2D向立体3D发展的主要代表产品,使DRAM开启了3D化道路。HBM是通过TSV技术进行芯片堆叠,以增加吞吐量并克服单一封装内带宽的限制。HBM能充分利用空间并缩小面积,并且突破了内存容量与带宽瓶颈。

据Yole的观点和预测,这种新颖的3D技术将在2029-2030年期间进入市场。在此之前,我们预计混合键合系统可能会开始渗透DRAM设备市场,用于制造3D堆叠DRAM,例如高带宽内存(HBM),可能从HBM3+一代开始。

写在最后

现在诸如数据中心、汽车、5G等对内存的需求越来越大,要求也越来越高,技术的演进也一直在滚滚向前。不同时代,不同需求下,这些存储厂商们总能研发出新的技术来满足时代的发展。当然新型存储也是时代发展的产物,它们不是为了取代现有的存储解决方案,而是在延迟、生产力等方面对现有的存储进行很好的补充。最后说一句,存储是不得不发展的国家战略性高技术产业,我国应该抓住存储器技术发展多元化的新机遇,实现突破。