本文来自微信公众号“半导体行业观察”,作者/semianalysis。

生成式人工智能即将到来,它将改变世界。自从ChatGPT席卷全球并激发了我们对人工智能可能性的想象力以来,我们看到各种各样的公司都在争先恐后地训练人工智能模型并将生成式人工智能部署到内部工作流程或面向客户的应用程序中。不仅仅是大型科技公司和初创公司,许多财富500强非科技公司也在研究如何部署基于LLM的解决方案。

当然,这需要大量的GPU计算。GPU的销量像火箭一样猛增,而供应链却难以满足对GPU的需求。公司正在争先恐后地获得GPU或云实例。

即使OpenAI也无法获得足够的GPU,这严重阻碍了其近期路线图。由于GPU短缺,OpenAI无法部署其多模态模型。由于GPU短缺,OpenAI无法部署更长的序列长度模型(8k与32k)。

与此同时,中国公司不仅投资部署自己的LLM,还在美国出口管制进一步收紧之前进行储备。例如,据新闻报道,中国公司字节跳动据称从Nvidia订购了价值超过10亿美元的A800/H800。

虽然数十万个专门用于人工智能的GPU有许多合法的用例,但也有很多情况是人们急于购买GPU来尝试构建他们不确定是否有合法市场的东西。在某些情况下,大型科技公司正试图赶上OpenAI和谷歌,以免落后。对于没有经过验证的商业用例的初创公司来说,有大量的风险投资资金。我们知道有十几家企业正在尝试利用自己的数据训练自己的LLM。最后,这也适用于沙特阿拉伯和阿联酋今年也试图购买数亿美元的GPU的国家。

尽管Nvidia试图大幅提高产量,但最高端的Nvidia GPU H100直到明年第一季度仍将售空。Nvidia每季度将增加400,000个H100 GPU的出货量。

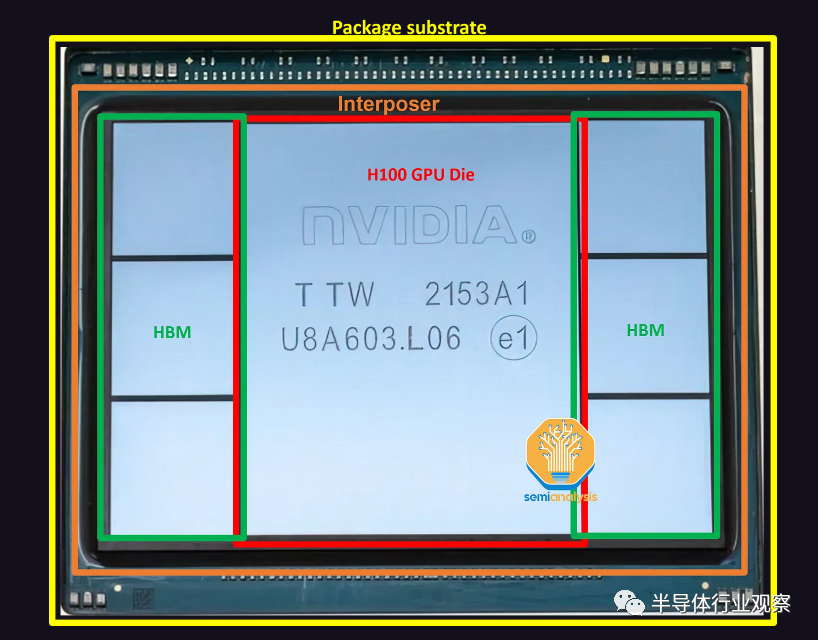

Nvidia的H100采用CoWoS-S上的7-die封装。中间是H100 GPU ASIC,其芯片尺寸为814mm2,周围是6个内存堆栈HBM。不同SKU之间的HBM配置有所不同,但H100 SXM版本使用HBM3,每个堆栈为16GB,总内存为80GB。H100 NVL将具有两个封装,每个封装上有6个活跃的HBM堆栈。

在只有5个激活HBM的情况下,非HBM芯片可以使用虚拟硅,为芯片提供结构支撑。这些芯片位于硅中介层的顶部,该硅中介层在图片中不清晰可见。该硅中介层位于封装基板上,该封装基板是ABF封装基板。

GPU Die和TSMC晶圆厂

Nvidia GPU的主要数字处理组件是处理器芯片本身,它是在称为“4N”的定制台积电工艺节点上制造的。它是在台积电位于台湾台南的Fab 18工厂制造的,与台积电N5和N4工艺节点共享相同的设施,但这不是生产的限制因素。

由于PC、智能手机和非AI相关数据中心芯片的严重疲软,台积电N5工艺节点的利用率降至70%以下。英伟达在确保额外的晶圆供应方面没有遇到任何问题。

事实上,Nvidia已经订购了大量用于H100 GPU和NVSwitch的晶圆,这些晶圆立即开始生产,远远早于运送芯片所需的晶圆。这些晶圆将存放在台积电的芯片组中,直到下游供应链有足够的产能将这些晶圆封装成完整的芯片。

基本上,英伟达正在吸收台积电的部分低利用率,并获得一些定价优势,因为英伟达已承诺进一步购买成品。

Wafer bank,也被称为die bank,是半导体行业的一种做法,其中存储部分处理或完成的晶圆,直到客户需要它们为止。与其他一些代工厂不同的是,台积电将通过将这些晶圆保留在自己的账簿上几乎完全加工来帮助他们的客户。这种做法使台积电及其客户能够保持财务灵活性。由于仅进行了部分加工,因此晶圆库中保存的晶圆不被视为成品,而是被归类为WIP。只有当这些晶圆全部完成后,台积电才能确认收入并将这些晶圆的所有权转让给客户。

这有助于客户修饰他们的资产负债表,使库存水平看起来处于控制之中。对于台积电来说,好处是可以帮助保持更高的利用率,从而支撑利润率。然后,随着客户需要更多的库存,这些晶圆可以通过几个最终加工步骤完全完成,然后以正常销售价格甚至稍有折扣的价格交付给客户。

HBM在数据中心的出现:

AMD的创新如何帮助Nvidia

GPU周围的高带宽内存是下一个主要组件。HBM供应也有限,但正在增加。HBM是垂直堆叠的DRAM芯片,通过硅通孔(TSV)连接并使用TCB进行键合(未来更高的堆叠数量将需要混合键合)。DRAM裸片下方有一颗充当控制器的基本逻辑裸片。

通常,现代HBM具有8层内存和1个基本逻辑芯片,但我们很快就会看到具有12+1层HBM的产品,例如AMD的MI300X和Nvidia即将推出的H100更新。

有趣的是,尽管Nvidia和Google是当今使用量最大的用户,但AMD率先推出了HBM。2008年,AMD预测,为了匹配游戏GPU性能而不断扩展内存带宽将需要越来越多的功率,而这些功率需要从GPU逻辑中转移出来,从而降低GPU性能。AMD与SK Hynix以及供应链中的其他公司(例如Amkor)合作,寻找一种能够以更低功耗提供高带宽的内存解决方案。这驱使SK海力士于2013年开发了HBM。

SK Hynix于2015年首次为AMD Fiji系列游戏GPU提供HBM,该GPU由Amkor进行2.5D封装。随后,他们在2017年推出了使用HBM2的Vega系列。然而,HBM并没有对游戏GPU性能产生太大的改变。由于没有明显的性能优势以及更高的成本,AMD在Vega之后重新在其游戏卡中使用GDDR。如今,Nvidia和AMD的顶级游戏GPU仍在使用更便宜的GDDR6。

然而,AMD的最初预测在某种程度上是正确的:扩展内存带宽已被证明是GPU的一个问题,只是这主要是数据中心GPU的问题。对于消费级游戏GPU,Nvidia和AMD已转向使用大型缓存作为帧缓冲区(large caches for the frame buffer),使它们能够使用带宽低得多的GDDR内存。

正如我们过去所详述的,推理和训练工作负载是内存密集型的。随着人工智能模型中参数数量的指数级增长,仅权重的模型大小就已达到TB级。因此,人工智能加速器的性能受到从内存中存储和检索训练和推理数据的能力的瓶颈:这个问题通常被称为“内存墙”。

为了解决这个问题,领先的数据中心GPU与高带宽内存(HBM)共同封装。Nvidia于2016年发布了首款HBM GPU P100。HBM通过在传统DDR内存和片上缓存之间找到中间立场,以容量换取带宽来解决内存墙问题。通过大幅增加引脚数以达到每个HBM堆栈1024位宽的内存总线,可以实现更高的带宽,这是每个DIMM 64位宽的DDR5的18倍。同时,通过大幅降低每比特传输能量(pJ/bit)来控制功耗。这是通过更短的走线长度来实现的,HBM的走线长度以毫米为单位,而GDDR和DDR的走线长度以厘米为单位。

如今,许多面向HPC的芯片公司正在享受AMD努力的成果。具有讽刺意味的是,AMD的竞争对手Nvidia作为HBM用量最大的用户,或许会受益最多。

HBM市场:SK海力士占据主导地位

作为HBM的先驱,SK海力士是拥有最先进技术路线的领导者。SK海力士于2022年6月开始生产HBM3,是目前唯一一家批量出货HBM3的供应商,拥有超过95%的市场份额,这是大多数H100 SKU所使用的。HBM现在的最大配置为8层16GB HBM3模块。SK Hynix正在为AMD MI300X和Nvidia H100刷新生产数据速率为5.6 GT/s的12层24GB HBM3。

HBM的主要挑战是存储器的封装和堆叠,这是SK海力士所擅长的,他们过去在这方面积累了最强大的工艺流程知识。

三星紧随Hynix之后,预计将在2023年下半年发货HBM3。我们相信它们是为Nvidia和AMD GPU设计的。他们目前在销量上与SK海力士存在很大差距,但他们正在紧锣密鼓地前进,并正在大力投资以追赶市场份额。三星正在投资以追赶并成为HBM市场份额第一,就像他们在标准内存方面一样。我们听说他们正在与一些加速器公司达成优惠协议,以试图获得更多份额。

他们展示了12层HBM以及未来的混合键合HBM。三星HBM-4路线图的一个有趣的方面是,他们希望在内部FinFET节点上制作逻辑/外围设备。这显示了他们拥有内部逻辑和DRAM代工厂的潜在优势。

美光科技在HBM方面排名垫底。

他们在混合存储立方体(HMC)技术上投入了更多资金。这是与HBM竞争的技术,其概念非常相似,大约在同一时间开发。然而,HMC周围的生态系统是封闭的,导致围绕HMC的IP很难开发。此外,还存在一些技术缺陷。HBM的采用率要高得多,因此HBM胜出,成为3D堆叠DRAM的行业标准。

直到2018年,美光才开始从HMC转向HBM路线图。这就是美光科技落在最后面的原因。他们仍然停留在HBM2E(SK海力士在2020年中期开始量产)上,他们甚至无法成功制造HBM2E。

在最近的财报电话会议中,美光对其HBM路线图做出了一些大胆的声明:他们相信,他们将在2024年凭借HBM3E从落后者变为领先者。HBM3E预计将在第三季度/第四季度开始为Nvidia的下一代GPU发货。

“我们的HBM3斜坡实际上是下一代HBM3,与当今业界生产的HBM3相比,它具有更高水平的性能、带宽和更低的功耗。该产品,即我们行业领先的产品,将从2024年第一季度开始销量大幅增加,并对24财年的收入产生重大影响,并在2025年大幅增加,即使是在2024年的水平基础上。我们的目标也是在HBM中获得非常强劲的份额,高于行业中DRAM的非自然供应份额。”美光首席商务官Sumit Sadana说。

他们希望在HBM中拥有比一般DRAM市场份额更高的市场份额的声明非常大胆。鉴于他们仍在努力大批量生产顶级HBM2E,我们很难相信美光声称他们将在2024年初推出领先的HBM3,甚至成为第一个HBM3E。在我们看来,尽管Nvidia GPU服务器的内存容量比英特尔/AMD CPU服务器要低得多,但美光科技似乎正在试图改变人们对人工智能失败者的看法。

我们所有的渠道检查都发现SK海力士在新一代技术方面保持最强,而三星则非常努力地通过大幅供应增加、大胆的路线图和削减交易来追赶。

真正的瓶颈-CoWoS

下一个瓶颈是CoWoS产能。CoWoS(Chip on Wafer on Substrate)是台积电的一种“2.5D”封装技术,其中多个有源硅芯片(active silicon)(通常的配置是逻辑和HBM堆栈)集成在无源硅中介层上。中介层充当顶部有源芯片的通信层。然后将中介层和有源硅连接到包含要放置在系统PCB上的I/O的封装基板。

HBM和CoWoS是互补的。HBM的高焊盘数(high pad count)和短走线长度要求需要CoWoS等2.5D先进封装技术来实现PCB甚至封装基板上无法实现的密集、短连接。CoWoS是主流封装技术,能够以合理的成本提供最高的互连密度和最大的封装尺寸。由于目前几乎所有HBM系统都封装在CoWoS上,并且所有高级AI加速器都使用HBM,因此,几乎所有领先的数据中心GPU都由台积电在CoWoS上封装。百度确实有一些先进的加速器,三星的版本也有。

虽然台积电(TSMC)的SoIC等3D封装技术可以将芯片直接堆叠在逻辑之上,但由于散热和成本的原因,这对于HBM来说没有意义。SoIC在互连密度方面处于不同的数量级,并且更适合通过芯片堆叠扩展片上缓存,如AMD的3D V-Cache解决方案所示。AMD的Xilinx也是多年前CoWoS的第一批用户,用于将多个FPGA小芯片组合在一起。

虽然还有一些其他应用使用CoWoS,例如网络(其中一些用于网络GPU集群,如Broadcom的Jericho3-AI)、超级计算和FPGA,但绝大多数CoWoS需求来自人工智能。与半导体供应链的其他部分不同,其他主要终端市场的疲软意味着有足够的闲置空间来吸收GPU需求的巨大增长,CoWoS和HBM已经是大多数面向人工智能的技术,因此所有闲置产能已在第一季度被吸收。随着GPU需求的爆炸式增长,供应链中的这些部分无法跟上并成为GPU供应的瓶颈。

“就在最近这两天,我接到一个客户的电话,要求大幅增加后端容量,特别是在CoWoS中。我们仍在评估这一点。”台积电首席执行官C.C Wei早起那说。

台积电一直在为更多的封装需求做好准备,但可能没想到这一波生成式人工智能需求来得如此之快。6月,台积电宣布在竹南开设先进后端Fab 6。该晶圆厂占地14.3公顷,足以容纳每年100万片晶圆的3D Fabric产能。这不仅包括CoWoS,还包括SoIC和InFO技术。有趣的是,该工厂比台积电其他封装工厂的总和还要大。虽然这只是洁净室空间,远未配备齐全的工具来实际提供如此大的容量,但很明显,台积电正在做好准备,预计对其先进封装解决方案的需求会增加。

稍微有帮助的是晶圆级扇出封装产能(主要用于智能手机SoC)的闲置,其中一些产能可以在某些CoWoS工艺步骤中重新利用。特别是,存在一些重叠的工艺,例如沉积、电镀、背面研磨、成型、放置和RDL形成,这将趋势设备供应链发生了有意义的转变。

虽然市场上还有来自英特尔、三星和OSAT(例如ASE的FOEB)提供的其他2.5D封装技术,但CoWoS是唯一一种大批量使用的技术,因为台积电是迄今为止最主要的AI加速器代工厂。甚至Intel Habana的加速器也是由台积电制造和封装的。然而,一些客户正在寻找台积电的替代品。

CoWoS拥有几种变体,但原始CoWoS-S仍然是大批量生产中的唯一配置。这是如上所述的经典配置:逻辑芯片+HBM芯片通过带有TSV的硅基中介层连接。然后将中介层放置在有机封装基板上。

硅中介层的一项支持技术是一种称为“reticle stitching”的技术。由于光刻工具slit/scan最大尺寸芯片的最大尺寸通常为26mm x 33mm。随着GPU芯片本身接近这一极限,并且还需要在其周围安装HBM,中介层需要很大,并且将远远超出这一标线极限。TSMC通过reticle stitching解决了这个问题,这使得他们能够将中介层图案化为标线限制的数倍(截至目前,AMD MI300最高可达3.5倍)。

CoWoS-R在具有重新分布层(RDL)的有机基板上使用,而不是硅中介层。这是一种成本较低的变体,由于使用有机RDL而不是硅基中介层,因此牺牲了I/O密度。正如我们所详述的,,AMD的MI300最初是在CoWoS-R上设计的,但我们认为,由于翘曲和热稳定性问题,AMD必须改用CoWoS-S。

CoWoS-L预计将在今年晚些时候推出,并采用RDL中介层,但包含嵌入中介层内部的用于芯片间互连的有源和/或无源硅桥。这是台积电相当于英特尔EMIB封装技术。随着硅中介层变得越来越难以扩展,这将允许更大的封装尺寸。MI300 CoWoS-S可能接近单硅中介层的极限。

对于更大的设计来说,使用CoWoS-L会更加经济。台积电正在开发6x reticle尺寸的CoWoS-L超级载具中介层。对于CoWoS-S,他们没有提到4x reticle之外的任何内容。这是因为硅中介层的脆弱性。这种硅中介层只有100微米厚,并且在工艺流程中随着中介层尺寸增大而存在分层或破裂的风险。