本文来自半导体产业纵横,作者/九林。

从一颗到量产,流片决定着芯片设计方案是否能用。每一次流片成功,都意味着一次成功的芯片设计。今年以来,国内诸多企业先后宣布芯片流片成功,这些成功无疑极大的证明国内芯片的进步。

国内GPU领域,沐曦首颗高性能通用GPU芯片宣布流片,采用7纳米工艺,预计2023年量产;景嘉微宣布其JM9系列第二款GPU已经完成流片、封装阶段工作;象帝先天钧一号GPU在今年6月进入流片。

汽车芯片领域,中颖电子正在研发车规级MCU,已流片成功,在验证阶段;国芯科技汽车域控制器芯片CCFC2016B已经完成流片;龙芯中科在接受机构调研时表示,其做了控制用的高可靠汽车MCU芯片,第一款已经流片;

SoC芯片领域,芯原科技已实现5nm系统级芯片(SoC)一次流片成功,多个5nm一站式服务项目正在执行;快手推出SL200自研SoC芯片,前已流片成功,正在进行线上内测。

接连不断的流片消息,国内芯片设计企业一直在闯“流片”关。

01

流片“定生死”

流片的重要性就在于,能够检验芯片设计是否成功。流片是芯片制造的关键环节,也就是将设计好的方案,交给芯片制造厂,现生产几片或者几十片样品,检测设计的芯片是否能够,或者是否需要进一步优化,如果能够生产出符合要求的芯片,那么就可以大规模生产了。

芯片流片的风险非常高。历史上,小米旗下松果电子的澎湃S2系列芯片因为连续五次的流片失败损失惨重。对于企业来说,流片失败意味着时间成本和资金都付诸东流,且下次流片结果依然未知。如果延误了产品上市的时间,在现在多变的市场中对于企业是极为致命的。

芯片设计的过程中有许多步骤,其中某一个步骤的失误都有可能造成流片失败。有芯片设计公司人士总结了芯片流片失败的原因:

第一,Design的版本拿错,尤其是ROM版本拿错,基本芯片就是废片;第二,出现一些无法利用软件绕开的BUG,比如在电源管理的时候,芯片在进入低功耗状态后无法退出,这类情况芯片虽然可以点亮,但是无法使用,属于重大失误;第三,对于安全要求非常高的芯片,如果出现硬件安全漏洞,软件无法规避的,那么芯片也算流片失败;第四,即使芯片功能达到要求,但是对于功耗要求低的物联网芯片,功耗过高也会属于流片失败。

总的来看,流片失败除了在硬件方面实际无法点亮外,没有达到功耗、电路、功能的要求都能判定流片失败。

在去年,地平线发布征程5芯片时,其创始人余凯自豪的宣布:“征程5芯片一次性流片成功。我们本来是准备了150小时的测试,结果15个小时全部通过。”地平线一次通过,可以看出其研究团队实力强劲。但是在芯片制造过程中,能够一次就流片成功的案例非常少,大多设计公司都需要经历多次流片。

有模拟芯片公司即使在团队完备、思路清晰的情况下,还是耗了8年时间,历经18次流片,才最终完成了传感器模拟计算IP验证,打造出了理想中的那颗“超低功耗、超近传感”芯片。

02

极力支持的流片政策

如此关键的环节,极为烧钱。某些更小的设计企业,也会在多次流片失败中宣布倒闭。有工程师表示:“我之前的公司就是被流片失败搞垮的。”

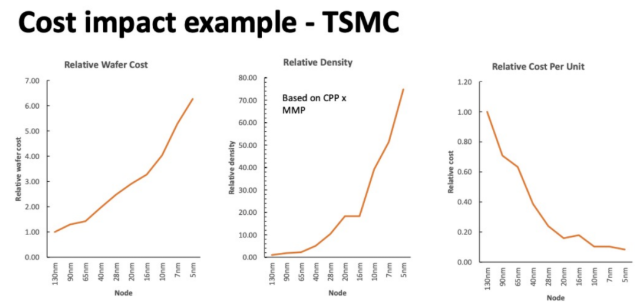

影响制造一颗成功芯片的因素非常多,包括采用什么样的工艺、多大尺寸的晶圆、芯片EDA的设计等,每一个环节的选择都会影响这颗芯片的流片成功率和成本。流片成本主要取决于半导体工艺,也就是芯片制程。随着半导体工艺的升级,芯片设计和流片费用都要呈指数级增长。

台积电成本影响示例

“千万级乃至上亿”去形容流片成本并不为过,据统计,最便宜的ASIC流片成本需要几十万一次,180nm的流片成本大概是50万元,55nm的成本在200万元,16nm成本就飙升到了3000万-5000万元,到了7nm最低也要过亿。

在中芯国际工作过的工程师分析了流片的过程和成本。芯片的成本分为两部分,一部分是Mask的成本,一部分是Wafer的成本。简单来说,费用=Mask制版费+N*单片晶圆成本。

在芯片设计完成后,会生产复杂的图片文件,一般来说会有30-50层,这些层需要在光罩厂做Mask(掩膜版)。工艺节点越高流片价格越贵,因为高工艺需要更多的Mask。例如在14nm制程上,需要60张Mask,而7nm就需要上百张Mask。

由于掩膜版每层的精度不同,光罩价格有些差异,但总体上40nm大约在30-50万美元,晶圆成本每片大约在1500-2000美元左右。因此,对于流片几片到几十片的设计厂来说,主要成本用于支付Mask。

由于流片生产的芯片数量少,30-50万美元的掩膜成本平摊到各个芯片来看,成本也极为高昂;但量产时将相同的掩膜成本平摊到十万片芯片上时,相对成本就低了很多。

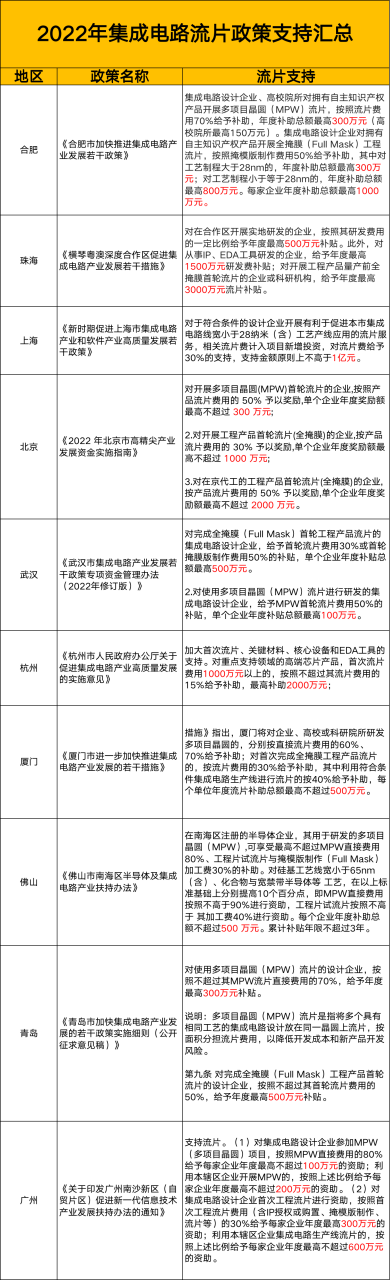

流片对于设计企业来说,确实是一大生死关,正因如此国内政府一直出台相应政策支持流片。实际上,从2000年时,我国财政部税务总局就已经通知海关总署,表示国内设计并具有自主知识产权的集成电路产品,因国内无法生产,到国外流片、加工,其进口环节增值税超过6%的部分实行即征即退。

在今年各省的十四五规划中,也都出现了对于流片的格外支持。

上海对于符合条件的设计企业开展有利于促进本市集成电路线宽小于28纳米(含)工艺产线应用的流片服务,相关流片费计入项目新增投资,对流片费给予30%的支持,支持金额原则上不高于1亿元。

北京对开展工程产品首轮流片(全掩膜)的企业,按产品流片费用的30%予以奖励,单个企业年度奖励额最高不超过1000万元;对在京代工的工程产品首轮流片(全掩膜)的企业,按产品流片费用的50%予以奖励,单个企业年度奖励额最高不超过2000万元。

横琴对开展工程产品量产前全掩膜首轮流片的企业或科研机构,给予年度最高3000万元流片补贴。

从流片支持力度来看,上海、苏州、杭州、合肥、珠海、广州等地给予补贴较大。其中,上海流片补贴最高额可达1亿元,珠海给予年度最高补贴3000万元。

03

MPW与Full Mask模式

为了解决高昂的流片价格,行业内也演变出两种流片方式Full Mask和MPW。

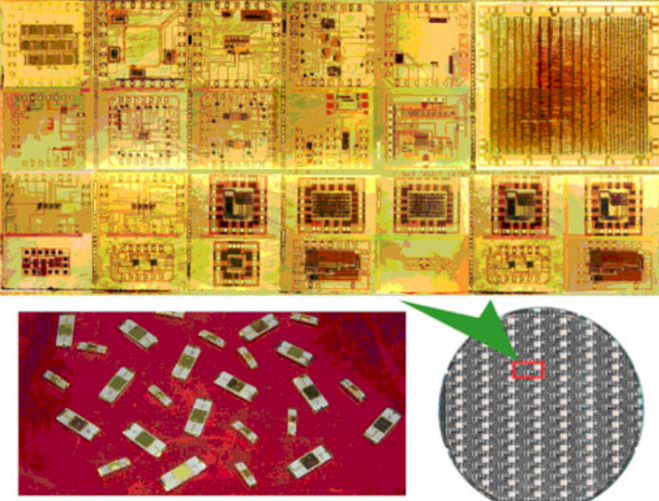

MPW(Multi Project Wafer)是很多小设计公司采用的流片方式。简单来说,MPW就是将多个具有相同工艺的集成电路设计放在同一圆片上流片,按面积分担流片费用。

业内人士表示:“Share Mask的好处就是省钱,但是由于你要等别人的数据都ready,所以需要更多的时间。通常大厂会自己利用一套Mask,毕竟30-50万对大厂来说不算太高;小公司偏向Share Mask,毕竟30-50万也不容易。”

下图是其MPW服务的一个示例,图中右下角的圆型是一个完整的6晶圆,用方框标出的矩形部分为MPW加工服务机构拼接后得到的中间数据,方框中的小矩形为不同设计公司设计的不同芯片。方框内部放大后如图的上半部分所示。图中左下角是封装后的集成电路芯片。实际加工时是将拼接后的矩形作为一个(虚拟)芯片,再进行流片制造。按照集成电路加工线的要求,通常一次加工必须制造一定数量的wafer(通常大于5片),因此一次MPW加工可以提供给设计公司足够多数量的样片。

代工厂每年固定实际(大多是Q4)会放出次年的MPW计划表,各家公司根据自己的需求报上车,一般来讲,越是先进的工艺安排的MPW频率越高,较为成熟的工艺,可能一年下来次数很少。

有IC设计厂的业内人士透露:“先进工艺下(55nm以下),一般是工艺厂来安排,事先会将晶圆划好ABCD等多个区域,并报价,各家公司根据自己情况去预订一个或多个区域,同时各家公司可以进一步选择在自己区域里放多个项目的测试片进去。(以LOGO区分)。”

一些大晶圆厂就会选择Full Mask模式。Full Mask就是指整个晶圆制造过程中的全部Mask都是为某个芯片所用,显然投片的成本非常高。但是这种方式可以将流片和后续量产缩短三个月左右时间。在与市场赛跑的过程中,更早的成品自然代表着更多的市场份额。

同时,国内一些直接采用Full Mask的设计厂,也是对自身开发能力的绝对自信。